El sistema de control digital de volcador de anodos de carbon es ahora representado en codigo VHDL, lo que permite analizar las ventajas y desventajas de ambos metodos (simbolico, vhdl) para el diseño de sistemas digitales.

Sistema Volcador de Anodos de Carbon

A continuación se presenta la implementación de un sistema de control digital utilizando el Software Quartus II de Altera. El sistema, utilizado en la empresa del aluminio, se encarga de colocar en posición vertical los ánodos de carbón utilizados en el proceso de reducción, para su transportación a las fosas de cocción. Debido a la disposición horizontal en la que provienen los ánodos del proceso de vibrocompactación, donde son formados, es necesario realizar el volcamiento para disponerlos en forma vertical, debido a que esto mejora el proceso de cocción y da una mejor consistencia al ánodo. Para este proceso se implementa un sistema mecánico que puede ser controlado por un sistema digital, implementado con Circuitos Digitales Configurables.

Objetivo

Realizar el control del Volcador de ánodos de carbón, utilizando un sistema de control digital, mediante lenguaje VHDL, con la ayuda del software Quartus II de Altera.

Descripción del Proceso

El sistema volcador de ánodos de carbón esta compuesto por sistemas mecánicos de arrastre y empuje y sensores electrónicos para la detección de objetos. En la siguiente figura se muestra la composición del sistema.

Sistema volcador de anodos de carbon

Entre los sensores electrónicos utilizados para controlar el sistema están:

- SP_C1 (Fotoeléctrico): Detecta presencia de ánodos de carbón en el conveyor.

- SM_H y SM_V (Inductivos): Detectan la posición de la mesa (volcador), horizontal o vertical respectivamente.

- SP_C2 (Mecánico): Detecta presencia de ánodos de carbón dentro de la mesa (volcador).

- SE_AT y SE_AD (Inductivos): Detectan la posición del empujador neumático, atrás o adelante respectivamente.

- SF_1 y SF_2 (Fotoeléctrico y Mecánico): Detectan sistema full, paquete de ánodos formado.

Como salidas se tienen:

- Activación del conveyor (MC_ON), señal que activa el motor para mover los ánodos hacia la mesa (volcador).

- Señal VM_ON y VM_OFF, utilizadas para activar la mesa (volcador) hacia arriba y hacia abajo respectivamente.

- Señal EM_AD y EM_AT, utilizadas para activar el empujador hacia adelante y hacia atrás respectivamente.

Descripción del Funcionamiento:

- Al encenderse el sistema (ON=’1’), detectarse ánodos de carbón en el conveyor (SP_C1=’1’), y las condiciones de: mesa en posición horizontal (SM_H=’1’) y descargada (SP_C2=’0’) se comienzan a desplazar los ánodos hacia el volcador, hasta que uno de ellos este dentro del mismo.

- Cuando se detecta el ánodo dentro del volcador (SP_C2=’1’) se detiene el conveyor, posteriormente se da la orden de subir la mesa (volcador) hasta que se posiciona verticalmente (SM_V=’1’). Esto ocurre siempre y cuando el empujador este en posición atrás (SE_AT=’1’). Una vez colocado en posición vertical el ánodo, se activa el empujador (EM_AD=’1’) para sacar el ánodo del volcador hasta que el empujador llega a la posición adelante (SE_AD=’1’).

- Posteriormente, una vez que se activa el regreso del empujador (EM_AT=’1’) y que este llega a la posición atrás (SE_AT=’1’), se activa la señal para bajar la mesa (VM_OFF=’1’) hasta que esta llega a la posición horizontal (SM_H=’1’). Luego, al estar nuevamente las condiciones, se repite el proceso.

- Si la señal de ON=’0’, el sistema se detiene. Igualmente si el sistema se llena (esta formado el paquete de seis ánodos a la salida del volcador), se activan las señales de full (SF_1=SF_2=’1’), es detenido el conveyor para evitar que se introduzcan mas ánodos de carbón al volcador.

Todo lo anterior puede observarse en la tabla logica y ecuaciones digitales para el funcionamiento del sistema.

Tabla de la verdad y Ecuaciones logicas

Tabla de la verdad y Ecuaciones logicas

Con la ayuda del la herramienta CAD Quartus de Altera, se puede entonces diseñar la logica digital para ser integrada en un chip que maneje el funcionamiento del sistema.

Diseño del código en Quartus II a partir de las ecuaciones lógicas

Para la implementación del circuito en Quartus II en VHDL, una vez definida la tabla y las ecuaciones lógicas, el siguiente paso es muy sencillo.

Para esto se procede, primeramente a la construcción de un nuevo proyecto:

- Se inicia el software Quartus II, File → New Project Wizard.

- Luego, paso a paso se va configurando el proyecto, Name, etc.

- A continuación se escoge el tipo de dispositivo, Family: FLEX10K, Available Devices: EPF10K10LC84-3

Para crear el código VHDL:

- Se selecciona File → New. En la ventana emergente se cambia a VHDL File. Luego OK. Aparecerá la ventana donde se desarrollara el código.

- Siguiendo la secuencia para el diseño con VHDL, primeramente se definen las librerías necesarias, la entidad, variables y la arquitectura del programa.

- Con la ayuda de los distintos elementos sintácticos del VHDL, a partir de la tabla lógico, se diseñan las distintas secuencias del programa. Sentencias lógicas IF y ELSIF funcionan como un elemento de memoria (Lacht), etc.

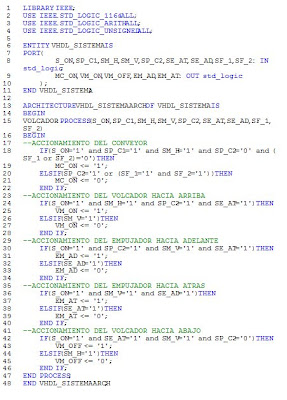

De acuerdo a lo anterior se desarrolla el código que se muestra en la figura a continuación.

Codigo VHDL del Sistema

Codigo VHDL del Sistema Asignación de Pines:

Siguiendo de igual forma el procedimiento aplicado para el diseño con Simbólico, se procede a la asignación de los pines.

- En el menú principal de Quartus II se selecciona Assignments → Pins.

- Al hacer doble click sobre uno de los pines del dispositivo, puede asignársele una de las señales de I/O definidas en el proyecto. Al asignar una señal de entrada, el pin correspondiente quedara definido con entrada. De igual manera para las señales de salida.

- Estos pasos se repiten para cada una de las señales definidas en el proyecto.

- Al terminar se presiona en OK.

- Posteriormente en Save, para salvar los cambios.

La asignación de pines se puede apreciar en la siguiente figura.

Asignacion de Pines en VHDL

Para compilar el proyecto:

- Se selecciona Processing → Start Compilation.

- Luego, si se recibe el mensaje: Full complication was successfull, se continúa con el proyecto. Si aparece cualquier error entonces debe verificarse hasta cumplir los pasos anteriores.

- Cerrar la ventana del compilador.

Para realizar la simulación:

- Para realizar la simulación en un tiempo de 0.0ns a 80.0ns, se selecciona Edit → End Time se define 80.0 ns en Time.

- Se selecciona View → Fit in Window para mostrar el rango completo de la simulación.

- Se selecciona Assignments → Settings para abrir la ventana de ajustes. Bajar a

Simulations Settings y cambiar Mode a Functional. - Ir a File → Save.

- Seleccionar el nombre del proyecto de simulación y click en OK.

- En el menu principal seleccionar Processing → Start Simulation.

- Al terminar la simulación hacer click en OK.

- Select View → Fit in Window para mostrar el rango complete de la simulación.

- Se simulan las diferentes situaciones y se verifica la activación de las salidas con respecto a la tabla de la verdad.

Resultados de la Simulación

Resultados de la SimulaciónAnalisis de Resultados y Conclusiones

De la creación del sistema en lenguaje VHDL se observa que presenta una forma mucho mas generalizada, tanto para la comprensión de diseñadores informáticos como electrónicos, ya que no exige la necesidad de conocer los elementos que deben conformar el diseño si no, mas bien el como debe ser su comportamiento de acuerdo a sus entradas.

Observando y analizando el cuadro de simulación anterior, se comprueba que el funcionamiento del sistema diseñado en VHDL es el esperado (de acuerdo a la tabla lógica). El periodo de funcionamiento que comienza, con la presencia de las condiciones iniciales necesarias, a los 10ns, se cumple de la forma esperada hasta los 63ns aproximadamente, donde comienza un nuevo ciclo.

En el momento de hacerse presentes las señales de sistema full (SF_1=SF_2=’1’) se nota como, aun estando las condiciones iniciales, no se produce el arranque del conveyor (MC_ON=’0’), lo que permite verificar el correcto funcionamiento del diseño.

No hay comentarios:

Publicar un comentario